AMD第五代EPYC“都灵”CPU曝光:采用Zen 5 Zen 5C混合架构,革新性进化助力性能无限提升!

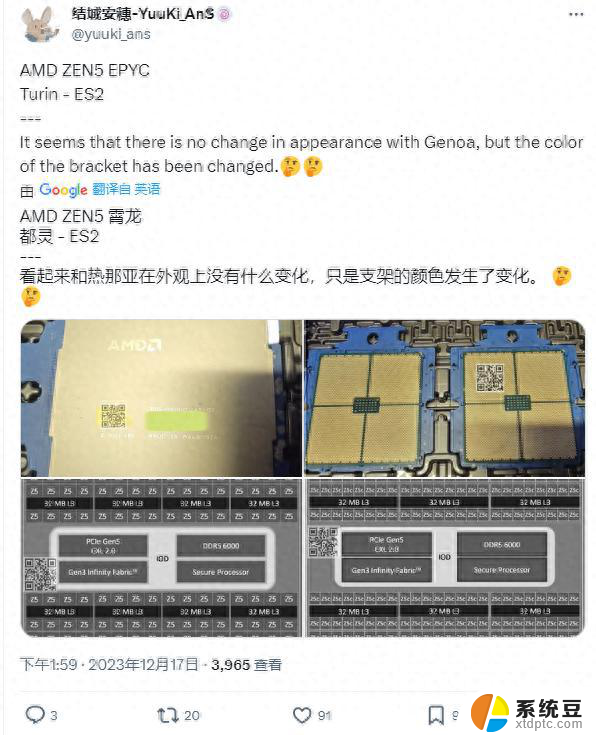

从图来看,这一代处理器设计变化不大,相比 Genoa 几乎没有太大变化,只是支架的颜色发生了改变预计,将会与 SP5 平台保持兼容性。

该系列处理器最多有 16 个 CCD,每个 CCD 带有 8 个物理核心以及独立的的 32 MB L3 缓存,最多 128 个核心和 256 个线程以及 512 MB 的 L3 缓存。与基于 Zen 4 的 Genoa 系列相比,该系列处理器增加了 33% 的核心数量以及 33% 的 L3 缓存。

都灵属于 AMD 第五代 EPYC 产品线,将用来取代当前第四代 EPYC 家族产品(Genoa、Genoa-X、Bergamo 和 Siena)。考虑到第四代 EPYC 处理器(9004/8004)使用了 Zen 4 + Zen 4C 混合架构,而第五代 EPYC 也将采用类似的 Zen 5(Nirvana) + Zen 5C(Prometheus)设计。

从 @结城安穗-YuuKi_AnS 给出的图片来看,这颗都灵 ES2 芯片生产于 2023 年,看起来非常新。

实际上,@Ditto_55 上个月已经给出了该系列处理器(内部代号为 Breithorn)的 OPN 代码,汇总如下:

100-000001245 -16 CCD + 1 IOD(128 个 Zen 5 核心 256 线程 512 MB 缓存)

100-000001341 -12 CCD + 1 IOD(96 个 Zen 5 核心 192 线程 384 MB 缓存)

100-000001247 -8 CCD + 1 IOD(64 个 Zen 5 核心 128 线程 256 MB 缓存)

100-000001342 -8 CCD + 1 IOD(64 个 Zen 5 核心 128 线程 256 MB 缓存)

100-000001249 - 2 CCD + 1 IOD(32 个 Zen 5C 核心 64 线程 64 MB 缓存)

与基于 Zen 4C 核心的 Bergamo 系列 CPU 相比,采用 Zen 5C 核心的 Turin 芯片核心和线程数将增加 50%(192/384 对 128/256),缓存数也将增加 50%(384 MB 对与 256 MB)。

AMD 已确认基于 Zen 5 架构的都灵 CPU 将于 2024 年推出,并将带来更强的单位功耗性能。从而对抗英特尔新一代的 Granite Rapids Xeon 芯片。

AMD第五代EPYC“都灵”CPU曝光:采用Zen 5 Zen 5C混合架构,革新性进化助力性能无限提升!相关教程

- 英特尔第五代数据中心CPU、Guadi 3加速器细节曝光:性能突破巅峰,引领数据中心技术革新!

- 骁龙8 Gen 4爆料:GPU显著升级 CPU性能略有提升,新一代骁龙处理器性能提升亮点揭秘

- 天玑9400正式发布 采用全大核CPU架构 跑分突破300万,性能强劲,值得期待

- 小身材,大能量!AMD车规级FPGA助力智能座舱再升级,性能提升显著

- AMD发布新显卡驱动:多项特性增强,性能提升明显

- Win10系统怎么优化性能和提升使用体验?最全面的优化指南

- 特斯拉座舱芯片或升级,AMD推出V2000A系列:革新车内体验与卓越性能共同融合

- 腾讯微软合作,Windows直接运行移动应用,助力用户体验提升

- 微软新版Forms应用:AI支持和多种表单主题助力,提升用户体验

- AMD下代Strix Halo APU曝光:搭载40个CU,横扫中端显卡,性能强劲无敌

- 6大国产CPU中,有3大,已经胜出了?这3款处理器性能如何?

- 英伟达新一代AI芯片过热延迟交付?公司回应:客户仍然抢购

- 国产CPU厂商迎来新一轮竞争:谁将成为行业领头羊?

- 如何查看电脑显卡型号和性能信息的详细步骤:快速了解你的电脑性能

- 涉嫌破坏市场竞争 美国监管部门要调查微软云服务,引发关注

- 高通骁龙855处理器是旗舰处理器吗?你搞明白了吗?

微软资讯推荐

- 1 6大国产CPU中,有3大,已经胜出了?这3款处理器性能如何?

- 2 英伟达新一代AI芯片过热延迟交付?公司回应:客户仍然抢购

- 3 国产CPU厂商迎来新一轮竞争:谁将成为行业领头羊?

- 4 高通骁龙855处理器是旗舰处理器吗?你搞明白了吗?

- 5 如何激活Windows系统,轻松解决电脑激活问题,一键激活教程分享

- 6 千千纯净Win11的“了解此图片”图标的神秘功能: 提升系统安全性的关键利器

- 7 2024年11月值得入手的CPU,总有一款适合你的购买指南

- 8 告别Windows 10,迎接Windows 11的七大革新,抓紧升级!

- 9 在韩国组装PC市场,AMD拿下了62%的市场份额,成为最受欢迎的处理器品牌

- 10 超微放弃NVIDIA NVL72 GB200芯片订单,台湾公司接手大额订单

win10系统推荐

系统教程推荐

- 1 美版iphone12pro和国版有什么区别 iphone12pro美版和国行的配置差异

- 2 怎么关闭百度的无痕浏览 取消百度浏览器无痕浏览的方法

- 3 windows开机很慢 win10开机破8秒的实用技巧

- 4 查询连接的wifi密码 电脑上查看WIFI密码步骤

- 5 qq输入法符号怎么打 QQ拼音输入法如何打出颜文字

- 6 如何将软件设置成开机自动启动 Win10如何设置开机自动打开指定应用

- 7 为什么设不了锁屏壁纸 Win10系统锁屏壁纸无法修改怎么处理

- 8 win10忘了开机密码怎么进系统 Win10忘记密码怎么办

- 9 电脑屏幕如何锁屏快捷键 电脑锁屏的快捷键是什么

- 10 打印机脱机如何解决 打印机脱机显示怎么办